WD4000国产晶圆几何形貌量测设备通过非接触测量,将晶圆的三维形貌进行重建,强大的测量分析软件稳定计算晶圆厚度,TTV、BOW、WARP、在高效测量测同时有效防止晶圆产生划痕缺陷。可实现砷化镓

2024-03-15 09:22:08

立錡推出的低压输入、CSP 小封装降压转换器系列,不仅满足各式小型穿戴式和 IoT 物联网应用的需求,更在性能和尺寸上取得了绝佳平衡。

2024-03-14 15:03:10 189

189 面对晶振频差不一样的情况时,需要满足以下条件才能进行替换:

1.频率范围:新晶振的频率范围必须覆盖旧晶振的频率范围。如果新晶振的频率范围过窄,可能无法满足设备的需求。

2. 封装尺寸:新晶振的封装尺寸

2024-03-04 13:48:39

WD4000无图晶圆几何形貌测量系统是通过非接触测量,将晶圆的三维形貌进行重建,强大的测量分析软件稳定计算晶圆厚度,TTV,BOW、WARP、在高效测量测同时有效防止晶圆产生划痕缺陷。可兼容不同材质

2024-02-21 13:50:34

WD4000无图晶圆几何形貌测量设备采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、Bow、Warp、TIR、SORI、等

2024-01-10 11:10:39

WD4000半导体晶圆厚度测量系统自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。1、使用光谱共焦对射技术测量晶圆Thickness、TTV、LTV、BOW、WARP、TIR

2024-01-09 09:08:07

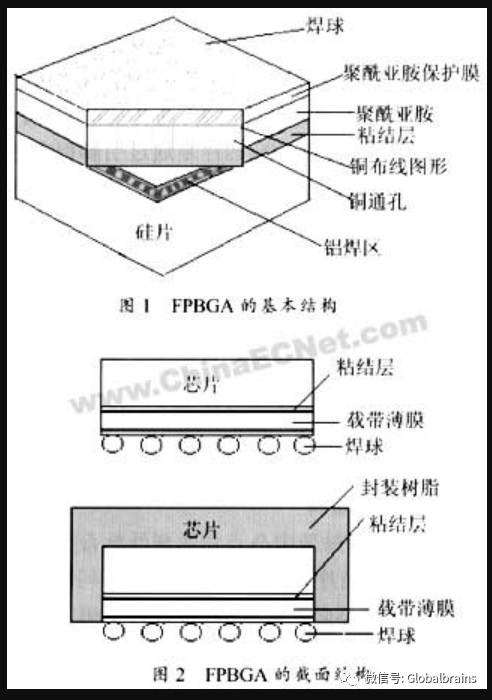

为了实现集成电路芯片的电通路,一般需要将芯片装配到在塑料或陶瓷载体上,这一过程可以称为CSP。CSP的尺寸只是略大于芯片,通常封装尺寸不大于芯片面积的1.5倍或不大于芯片宽度或长度的 1.2

2023-12-22 09:08:31 534

534

TC-Wafer是将高精度温度传感器镶嵌在晶圆表面,对晶圆表面的温度进行实时测量。通过晶圆的测温点了解特定位置晶圆的真实温度,以及晶圆整体的温度分布,同还可以监控半导体设备控温过程中晶圆发生的温度

2023-12-21 08:58:53

)及分析反映表面质量的2D、3D参数。广泛应用于衬底制造、晶圆制造、及封装工艺检测、3C电子玻璃屏及其精密配件、光学加工、显示面板、MEMS器件等超精密加工行业。WD

2023-12-20 11:22:44

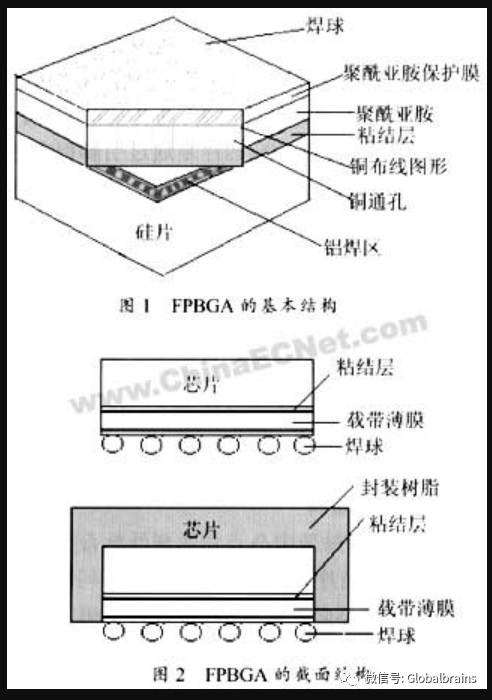

以来迅速发展的新型微电子封装技术,包括焊球阵列封装(BGA)、芯片尺寸封装(CSP)、圆片级封装(WLP)、三维封装(3D)和系统封装(SIP)等项技术。介绍它们的发展状况和技术特点。同时,叙述了微电子

2023-12-11 01:02:56

、ATX-H12和ATX-H13温补晶振(TCXO)系列特别适用于具有Wi-Fi、GPS和蓝牙服务的空间受限和功率受限的设备。这些设备为需要电信、导航和定位等功能的精确定时解决方案的应用提供了低至±2ppm的紧密

2023-12-07 09:30:19

国产有哪些FPGA入门?莱迪思半导体?高云半导体?

2023-12-05 16:05:38

晶圆测温系统tc wafer晶圆表面温度均匀性测温晶圆表面温度均匀性测试的重要性及方法 在半导体制造过程中,晶圆的表面温度均匀性是一个重要的参数

2023-12-04 11:36:42

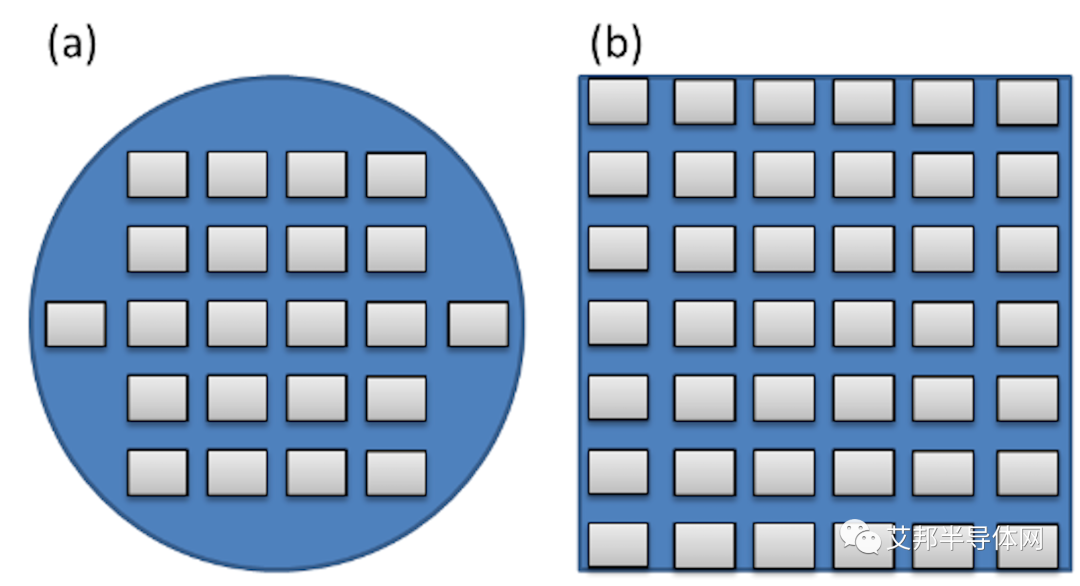

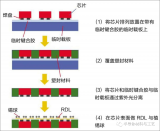

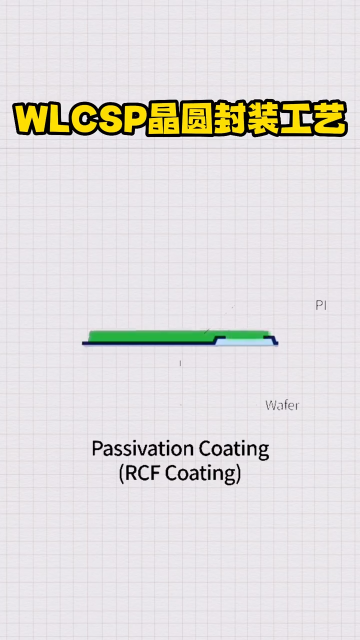

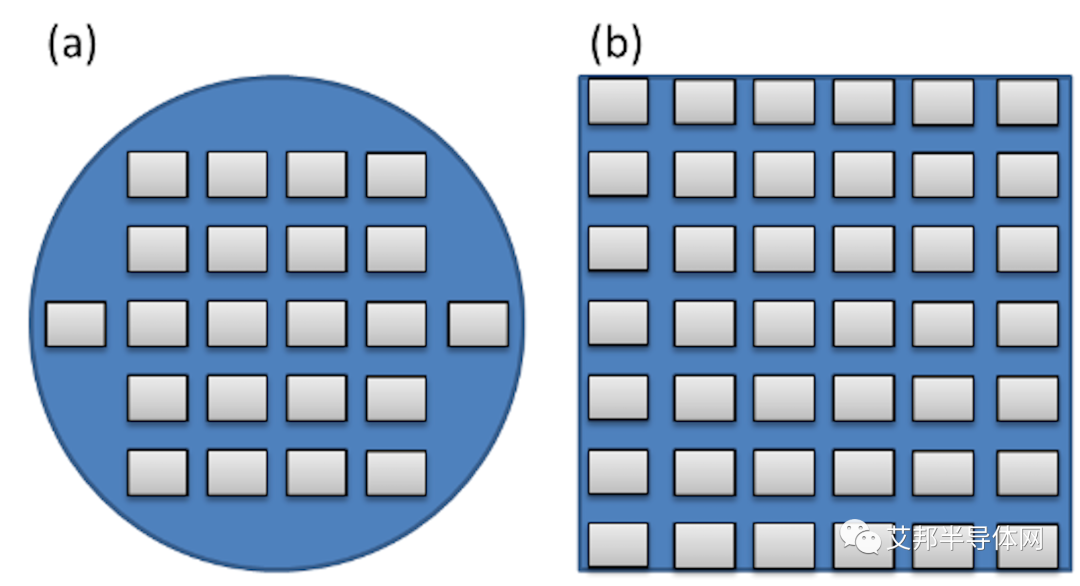

半导体封装方法,大致可以分为两种:传统封装和晶圆级(Wafer-Level)封装。传统封装首先将晶圆切割成芯片,然后对芯片进行封装;而晶圆级封装则是先在晶圆上进行部分或全部封装,之后再将其切割成单件。

2023-11-19 12:30:08 1014

1014 三星计划在2024年先进3D芯片封装技术SAINT(Samsung Advanced Interconnection Technology,三星高级互连技术),能以更小尺寸的封装,将AI芯片等高性能芯片的内存和处理器集成。

2023-11-15 11:09:30 931

931 请问像AD8233一样的晶圆封装在PCB中如何布线,芯片太小,过孔和线路都无法布入,或者有没有其他封装的AD8233

2023-11-14 07:01:48

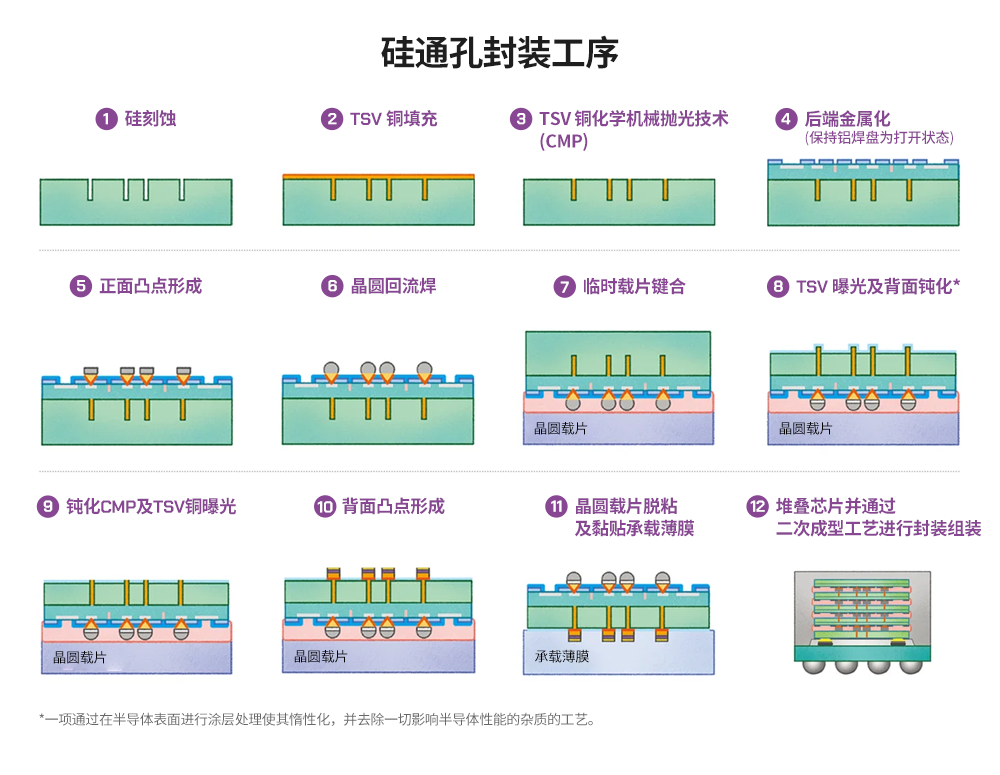

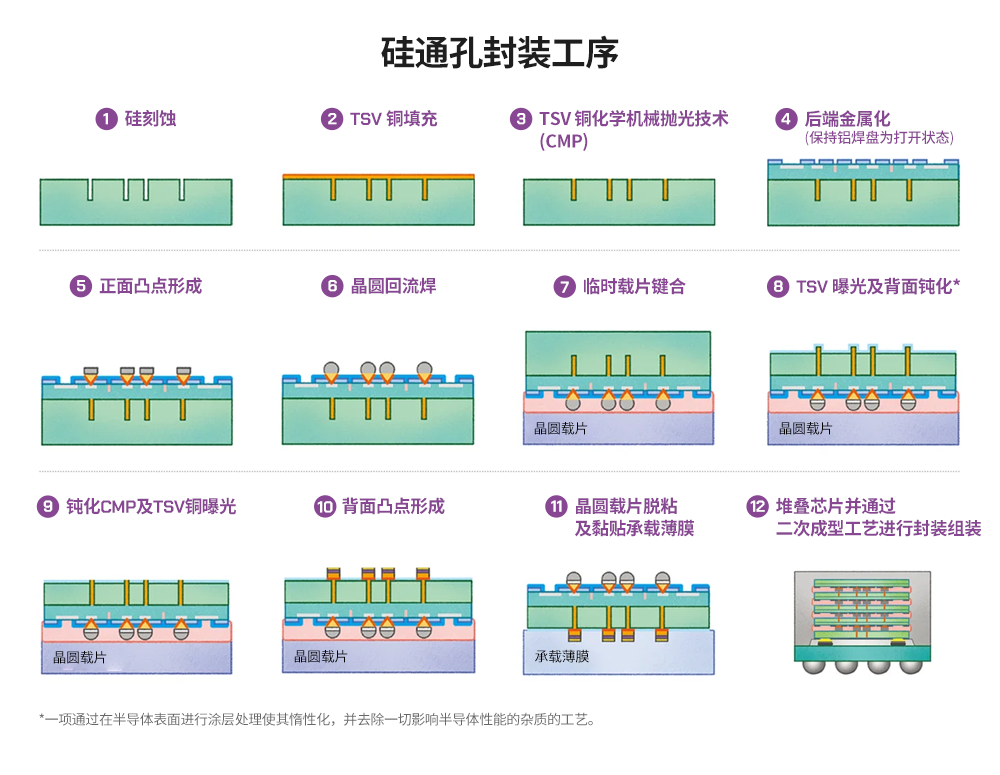

在上篇文章中介绍了扇入型晶圆级芯片封装(Fan-In WLCSP)、扇出型晶圆级芯片封装(Fan-Out WLCSP)、重新分配层(RDL)封装、倒片(Flip Chip)封装,这篇文章着重介绍硅通孔(TSV)封装工艺。

2023-11-08 10:05:53 1825

1825

介绍了晶圆级封装的基本流程。本篇文章将侧重介绍不同晶圆级封装方法所涉及的各项工艺。晶圆级封装可分为扇入型晶圆级芯片封装(Fan-In WLCSP)、扇出型晶圆级芯片封装(Fan-Out WLCSP

2023-11-08 09:20:19 2746

2746

WLCSP(Wafer Level Chip Scale Packaging)即晶圆级芯片封装方式,不同于传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积),此种最新技术是先在整片晶圆上进行封装和测试,然后才切割成一个个的IC颗粒,因此封装后的体积即等同IC裸晶的原尺寸。

2023-11-06 11:02:07 1026

1026

WD4000晶圆几何形貌测量及参数自动检测机通过非接触测量,将晶圆的三维形貌进行重建,强大的测量分析软件稳定计算晶圆厚度,TTV,BOW、WARP、在高效测量测同时有效防止晶圆产生划痕缺陷

2023-11-06 10:49:18

WD4000系列半导体晶圆几何形貌自动检测机采用高精度光谱共焦传感技术、光干涉双向扫描技术,完成非接触式扫描并建立3D Mapping图,实现晶圆厚度、TTV、LTV、Bow、Warp、TIR

2023-11-06 10:47:07

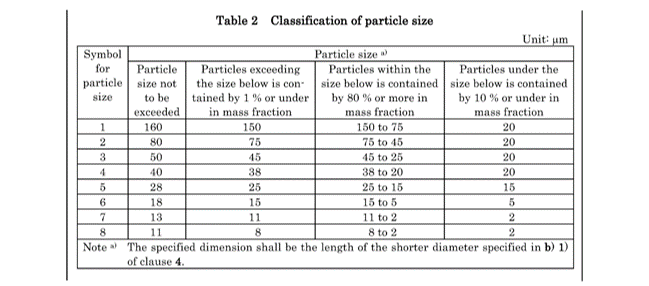

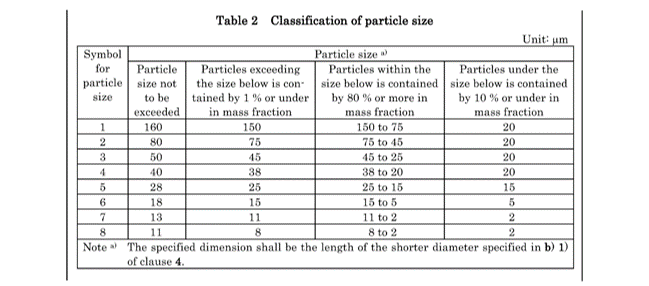

介绍微型芯片封装如何选择合适的焊粉尺寸?

2023-10-27 10:17:40 207

207

WD4000半导体晶圆表面三维形貌测量设备自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。可广泛应用于衬底制造、晶圆制造、及封装工艺检测、3C电子玻璃屏及其精密配件、光学加工、显示

2023-10-23 11:05:50

WD4000半导体晶圆检测设备自动测量Wafer厚度、表面粗糙度、三维形貌、单层膜厚、多层膜厚。1、使用光谱共焦对射技术测量晶圆Thickness、TTV、LTV、BOW、WARP、TIR、SORI

2023-10-19 11:08:24

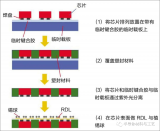

晶圆级封装是指晶圆切割前的工艺。晶圆级封装分为扇入型晶圆级芯片封装(Fan-In WLCSP)和扇出型晶圆级芯片封装(Fan-Out WLCSP),其特点是在整个封装过程中,晶圆始终保持完整。

2023-10-18 09:31:05 1339

1339

WD4000无图晶圆几何量测系统自动测量 Wafer 厚度 、表面粗糙度 、三维形貌 、单层膜厚 、多层膜厚 。使用光谱共焦对射技术测量晶圆 Thickness 、TTV 、LTV 、BOW

2023-10-18 09:09:00

麒麟a2芯片尺寸是多少 麒麟a2芯片尺寸是多少这个问题目前没有相关官方的报道,因此无法给出准确的回答。麒麟A2是华为旗下的音频芯片,麒麟A2芯片功耗相比上一代直接降低了50%,真正实现了高性能

2023-10-17 16:20:31 930

930 MINI USB接口尺寸封装集合

2023-09-28 07:16:45

扇出型晶圆级封装技术采取在芯片尺寸以外的区域做I/O接点的布线设计,提高I/O接点数量。采用RDL工艺让芯片可以使用的布线区域增加,充分利用到芯片的有效面积,达到降低成本的目的。扇出型封装技术完成芯片锡球连接后,不需要使用封装载板便可直接焊接在印刷线路板上,这样可以缩短信号传输距离,提高电学性能。

2023-09-25 09:38:05 756

756

定义:它是在基板的下边按面阵方式引出球形引脚,在基板上面贴装LSI芯片,是LSI芯片常用的-种表面贴装型封装形式。

2023-09-22 10:49:27 1176

1176

电子发烧友网站提供《32位单片机晶圆级芯片尺寸封装(WLCSP).pdf》资料免费下载

2023-09-19 16:12:26 0

0 电子发烧友网站提供《32位单片机晶圆级芯片尺寸封装(WLCSP).pdf》资料免费下载

2023-09-19 14:23:37 0

0 器件制造具有以下优点[1]

(1) 片子平面的总体平面度: CMP 工艺可补偿亚微米光刻中步进机大像场的线焦深不足。

(2) 改善金属台阶覆盖及其相关的可靠性: CMP工艺显著地提高了芯片测试中的圆片成品率。

(3) 使更小的芯片尺寸增加层数成为可能: CMP技术允许所形成的器件具有更高的纵横比。

2023-09-19 07:23:03

01CW24x系列串行EEPROM具有低引脚数、高可靠性、多种存储容量用于灵活的参数管理和小代码存储,满足稳定的数据保存、低功耗和空

02间受限的需要

03采用华虹95nm最先进工艺,晶圆CP测试

2023-09-15 08:22:26

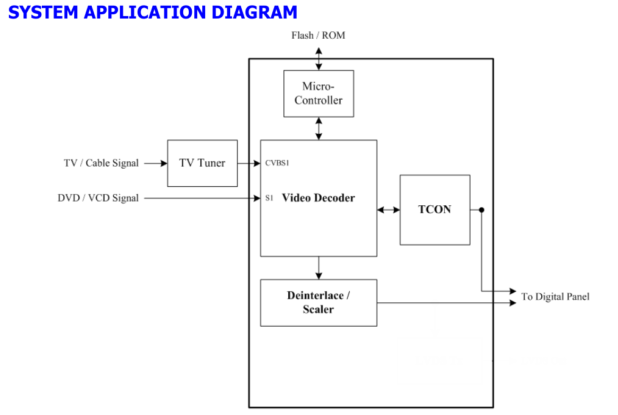

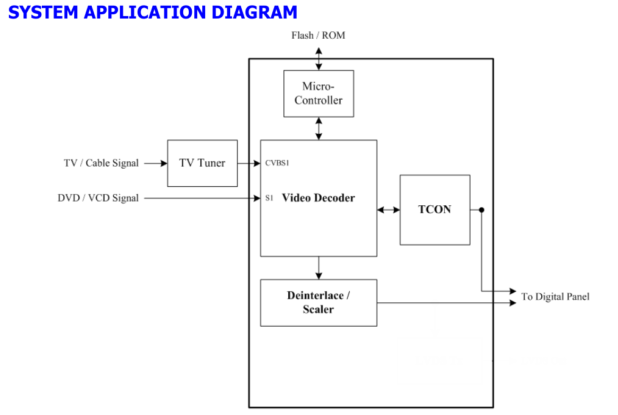

SSD101是SigmaStar推出的用于驱动小尺寸TTL-RGB接口液晶屏的方案,价格在10元人民币左右,性价比非常高,一般应用于车载显示驱动,可视门铃,以及一些只需要CVBS(AV)输入的驱动小尺寸液晶显示产品中,芯片尺寸小,只有64个脚,功耗低,还可以电池供电。

2023-09-13 15:19:23 994

994

所谓芯片尺寸封装就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美国EIA协会联合电子器件工程委员会)的JSTK一012标准规定,LSI芯片封装

2023-09-06 11:14:55 565

565

PFA花篮(PFA wafer Cassette) 又名 清洗花蓝 ,铁氟龙卡匣 , 铁氟龙晶舟盒 ,铁氟龙晶圆盒为承载半导体晶圆片/硅片

2023-08-29 08:57:51

DA14580 DEVKT -Pro 子板 WLCSP34 Electrical 原理图

2023-07-06 19:41:40 0

0 PLD是可编程逻辑器件(Programmable Logic Device)的缩写。它是一种集成电路芯片,具有可编程的逻辑功能。PLD可以根据用户需求进行编程,实现特定的逻辑功能和电路设计。

2023-07-05 15:50:35 2551

2551 晶圆测温系统,晶圆测温热电偶,晶圆测温装置一、引言随着半导体技术的不断发展,晶圆制造工艺对温度控制的要求越来越高。热电偶作为一种常用的温度测量设备,在晶圆制造中具有重要的应用价值。本文

2023-06-30 14:57:40

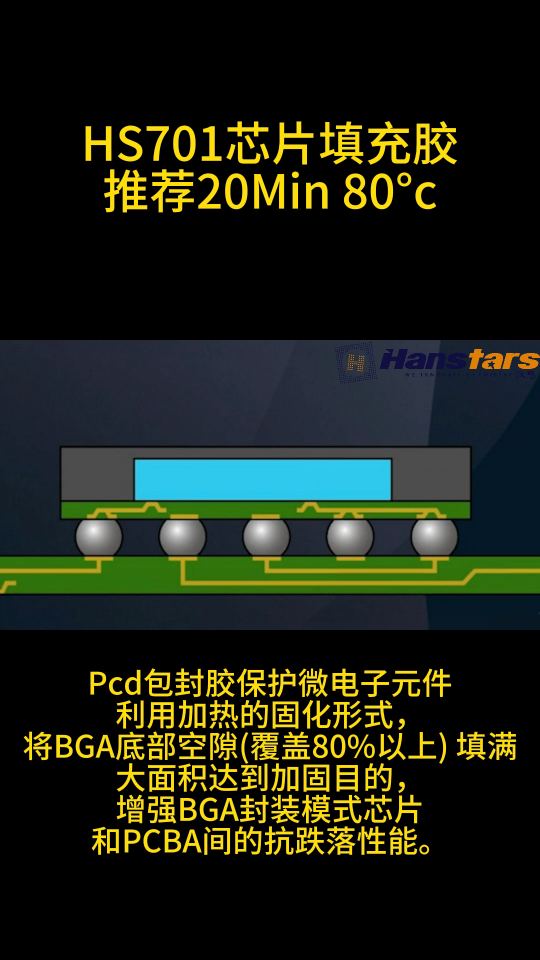

射频电子标签qfn芯片封装用底部填充胶由汉思新材料提供客户产品:射频电子标签。目前用胶点:qfn芯片加固。芯片尺寸:0.8MM*1.3MM客户要求:目前客户可以接受加热。颜色目前暂时没有要求

2023-06-30 14:01:42 553

553

PLD系列准分子激光器采用不同激光介质,如气体、液体或固体。通过在介质中产生激发态粒子,然后通过受激辐射过程产生激光。

2023-06-29 11:28:03 287

287

不同封装的晶振,有什么差别没有

2023-06-26 06:09:47

今天我们来介绍PLCSP(Panel Level Chip Scale Packaging)。同理,PLCSP是一种将面板级封装(PLP)和芯片尺寸封装(CSP)合为一体的封装技术。芯片尺寸封装(CSP)是指整个package的面积相比于silicon总面积不超过120%的封装技术。

2023-06-19 11:31:46 864

864

在计算焊盘坐标时,数据手册中指定的芯片尺寸与从晶圆上切割后的物理芯片尺寸之间经常存在混淆。芯片的物理边缘不是引线键合的良好参考,因为整体芯片尺寸略有不一致。本应用笔记将简要讨论芯片尺寸、芯片方向、键合坐标以及如何计算物理芯片尺寸。MAX3970将作为示例。

2023-06-16 17:23:19 370

370 ①须包括以下参数:管脚间距、芯片尺寸、厚度等;

②测试的参数指标:温度、频率、电流、电压的等;

2023-06-13 09:17:30 427

427

芯片功能测试常用5种方法有板级测试、晶圆CP测试、封装后成品FT测试、系统级SLT测试、可靠性测试。

2023-06-09 16:25:42

从理论上讲,环形电感器的封装尺寸可以是多种多样的,不同电性能的环形电感器的封装尺寸也可以是相同的。目前,市场上常规的环形电感器的包装尺寸相对固定。当然,这里提到的固定不仅仅意味着单个封装尺寸,而是具有相同电性能的环形电感器的封装尺寸基本相同。一般来说,制造商不太可能调整常规环形电感器封装尺寸。

2023-05-26 16:26:35 2

2 我们正在开发基于 imx8mp 处理器的产品。它通过 i2c 总线将程序加载到莱迪思 CrossLink FPGA。FPGA 二进制数据大小(.ied 文件)为 149KB,使用 400 KHz

2023-05-16 06:28:53

控制与安全,是莱迪思(Lattice)MachXO系列FPGA最鲜明的“标签”。从侧重于控制功能的MachXO/MachXO2/MachXO3,到行业第一颗安全控制FPGA芯片MachXO3D和具备

2023-05-12 09:45:04 719

719

半导体大规模生产过程中需要在晶圆上沉积集成电路芯片,然后再分割成各个单元,最后再进行封装和焊接,因此对晶圆切割槽尺寸进行精准控制和测量,是生产工艺中至关重要的环节。

2023-05-09 14:12:38

先进物联网解决方案的领先供应商橙群微电子,很高兴地宣布,其获奖的NanoBeaconSoCIN100采用突破性的晶圆级芯片规模封装(WLCSP)。这种新的封装尺寸

2023-05-09 11:43:56 983

983

先进物联网解决方案的领先供应商橙群微电子,很高兴地宣布,其获奖的NanoBeacon SoC IN100采用突破性的晶圆级芯片规模封装(WLCSP)。这种新的封装尺寸为1.1mm x 2.0mm

2023-05-09 09:56:58 408

408

圆片级芯片尺寸封装(WLCSP)是指在圆片状态下完成再布线,凸点下金属和焊锡球的制备,以及圆片级的探针测试,然后再将圆片进行背面研磨减薄

2023-05-06 09:06:41 1846

1846

FC-CSP 是芯片级尺寸封装(CSP)形式中的一种。根据J-STD-012 标准的定义口,CSP 是指封装体尺寸不超过裸芯片 1.2倍的一种封装形式,它通过凸块与基板倒装焊方式实现芯片与基板的电气

2023-05-04 16:19:13 2497

2497

半导体大规模生产过程中需要在晶圆上沉积集成电路芯片,然后再分割成各个单元,最后再进行封装和焊接,因此对晶圆切割槽尺寸进行精准控制和测量,是生产工艺中至关重要的环节。

2023-04-28 17:41:49

封装技术已经不能满足现状。而随着前端努力更好地缩小芯片尺寸,一个全新的技术领域出现了,那就是对先进封装技术的重视。那么进口芯片是如何封装的。进口芯片的封装方法。下面安玛科技小编为大家详细讲解。 对进口芯片进

2023-04-26 18:04:43 637

637

莱迪思凭借MachXO系列FPGA在控制功能方面长期处于领先地位。这些FPGA为当今数据中心、通信基础设施和工业系统不断增长的计算需求提供了理想的低功耗解决方案。

2023-04-25 14:46:52 207

207

莱迪思发布先进的系统控制FPGA - MachXO5T-NX继续加强低功耗FPGA产品系列

2023-04-23 14:22:15 184

184 微产品封装规格已近50种,品种超过7000个型号。在系统级封装领域,晶导微已攻克了不少核心技术,比如实现量产的反极性芯片制造工艺,掌握了高密度、低应力的IC框架设计以及专门针对多芯片引脚和PAD

2023-04-14 16:00:28

合封芯片是一种芯片封装技术,它将多个芯片通过引线相互连接在一起,形成一个更大的芯片结构,以便更好地实现集成和减小芯片尺寸。合封芯片的优点是可以提高芯片的集成度和性能,同时可以减小芯片尺寸,从而提高芯片的功能密度和速度。

2023-04-11 14:09:04 989

989 ,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。)

2.高传输速度(与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。)

3.高密度连接(WLP可运用数组式连接,芯片

2023-04-06 17:50:56 0

0 wafer晶圆GDP703202DG恒流1mA表压2Mpa裸片压力传感器die产品概述:GDP0703 型压阻式压力传感器晶圆采用 6 寸 MEMS 产线加工完成,该压力晶圆的芯片由一个弹性膜及集成

2023-04-06 14:48:12

在BGA封装加持下,APM32F407IGH6芯片在拥有同系列产品的功能配置和相同引脚数情况下,具备更高的引脚密度及更大的引脚间距,将芯片尺寸控制在10mm x10mm小尺寸,大大缩小了芯片所占空间,并有助于提高芯片成品率。

2023-04-01 15:09:10 668

668 BOARD MACHXO2 SENSOR EXTENDER

2023-03-30 12:04:42

LPDDR-SDRAM CTRLR FOR MACHXO2

2023-03-30 12:02:09

LPDDR-SDRAM CTRLR FOR MACHXO2

2023-03-30 12:01:19

KIT DEVELOPMENT MACHXO2 PICO

2023-03-30 11:49:35

KIT DEVELOPMENT MACHXO2 PICO

2023-03-30 11:49:24

BOARD MACHXO2 IMAGE INTERFACE

2023-03-29 22:50:33

ADAPTER 256-BGA MACHXO2

2023-03-29 22:44:47

ADAPTER SOCKET MACHXO2 184CSBGA

2023-03-29 22:44:47

SOCKET ADAPTER MACHXO2 332CABGA

2023-03-29 22:44:43

ADAPTER 256-FTBGA MACHXO2

2023-03-29 22:44:42

ADAPTER FOR MACHXO2 64UCBGA

2023-03-29 22:44:38

SOCKET ADAPTER FOR MACHXO2 32QFN

2023-03-29 22:44:33

电子发烧友App

电子发烧友App

评论